详细信息

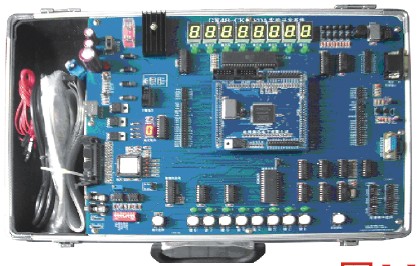

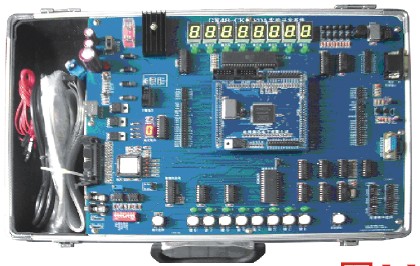

GW48-CK+型EDA实验开发系统介绍

EDA实验开发系统:GW48-CK+(完整系统)

配置、功能与特点:

□ 含Multi-task Reconfiguration电路结构(多功能重配置结构)。

□ 适配板GWA1C3)Cycline FPGA EP1C3T144,15万门、EPCS1 FPGA配置Flash,10万次编程周期。

□ 能对不同公司(Altera、Xilinx,lattice等)FPGA/CPLD进行实验开发;

□ FPGA/CPLD万能接插口;智能译码模块 ;±12V、5V、3.3V、2.5V、1.2V混合电压源;

□ 1Hz—50MHz标准时钟源;数字频率计;

□ VGA、UART、PS/2、FPGA/单片机等接口;

□ ADC和DAC;311构成的A/D;

□ 良好电磁兼容性的SX8200-J高速高密主板;

□ 用于信号发生器实验的有源滤波;

□ 可配模拟EDA器件适配板(ispPAC)

□ BytBlastII JTAG编程下载器,和ByteblasterMV编程下载器,能对不同公司的FPGA/CPLD实验开发;